该项目获得“第八届全国高校电工电子基础课程实验教学案例设计竞赛”一等奖,作者为长江师范学院的郝正同老师。下面为该作品的部分内容,完整内容请点击以下链接:

作品链接:https://pan.baidu.com/s/18S4kDg0ifuiGGPRjqJpbdA

提取码: dswz

一、实验案例简述

实验项目:集成计数器的验证与应用

概述:该实验项目是《数字电子技术实验》课程的一个典型时序逻辑电路实验。近年来,虚拟仿真技术和EDA技术逐渐深入融进《数字电子技术》课程的教学之中,传统的验证实验理应拓展为:典型数字器件逻辑功能验证和常用软件中对应数字器件模型的验证。然后方可在虚拟仿真软件中或EDA软件中应用被验证过的可靠模型设计给定的任务。

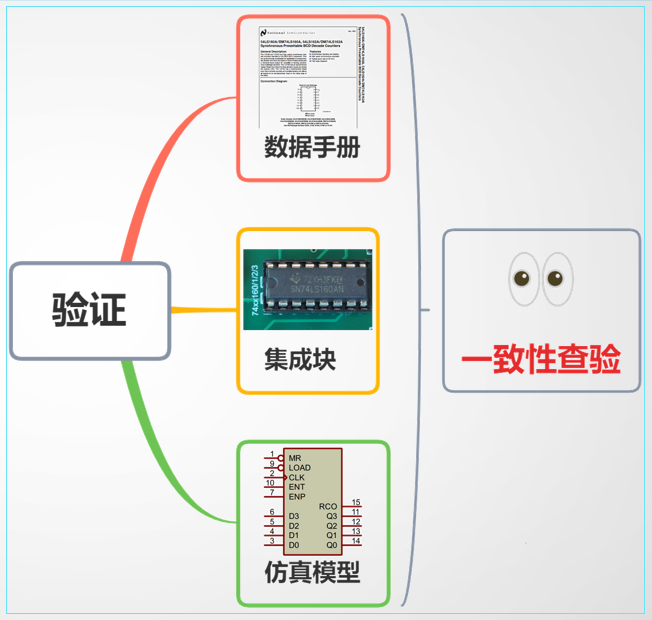

二、集成计数器的验证

通过实验手段查验集成块实物、仿真模型和数据手册间的逻辑关系是否一致。

三、集成计数器的应用

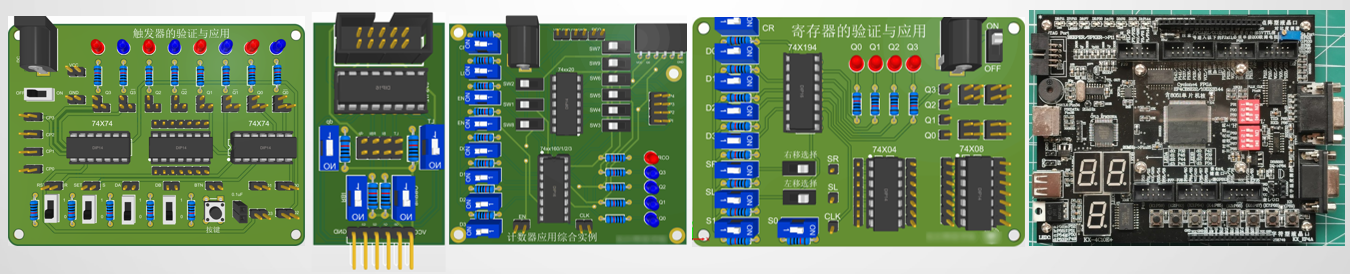

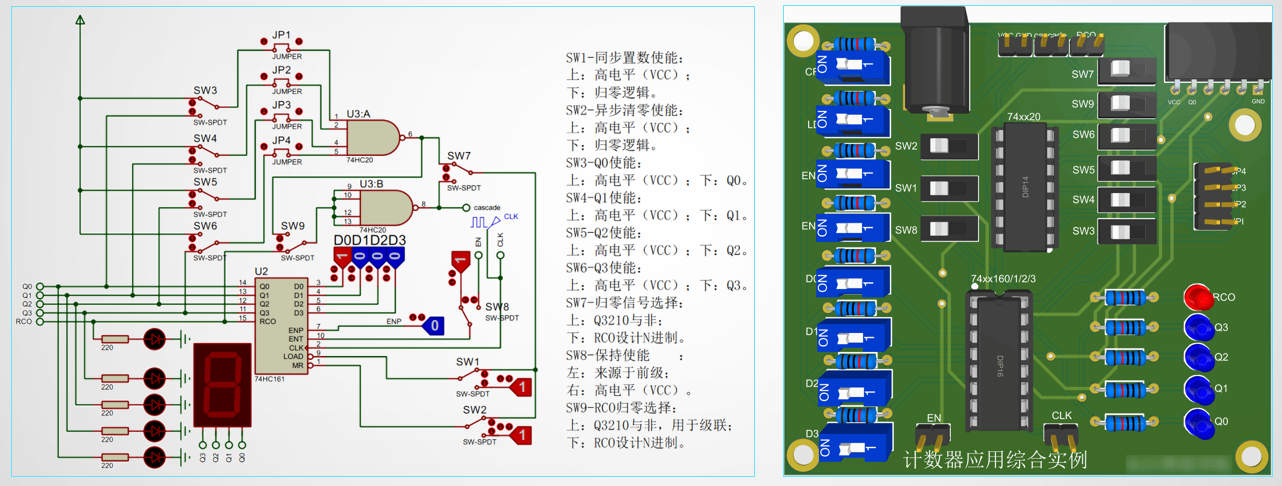

基于“计数器应用综合实例”口袋实验板(集成计数器使用74xx161)设计一个8进制加法计数器,并用74xx161进位输出端指示是否完成计数周期。

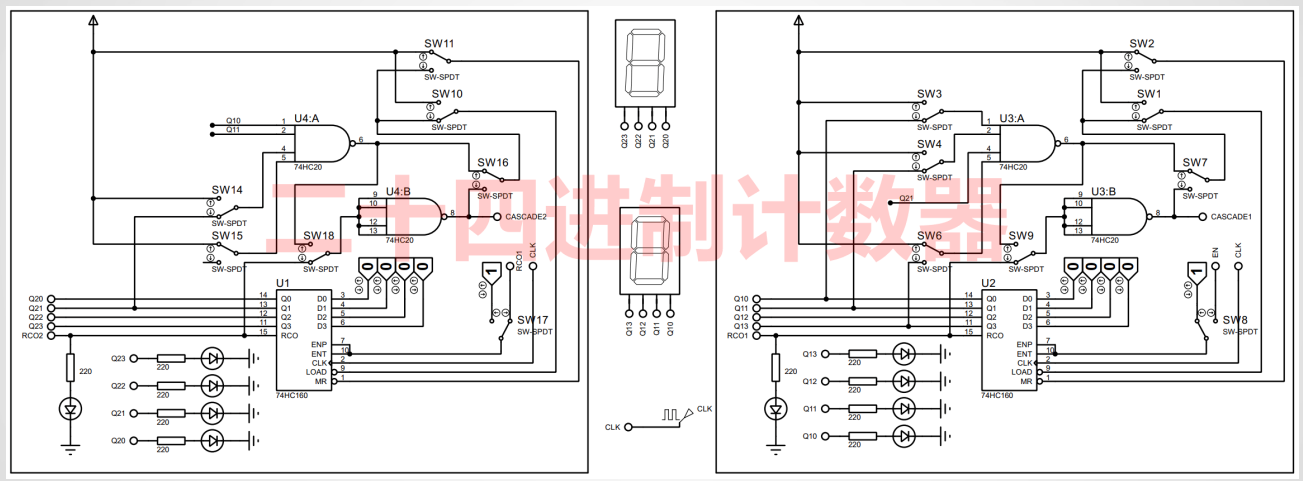

基于“计数器应用综合实例”口袋实验板(集成计数器使用74xx160)设计一个从2开始的8进制加法计数器。

四、基于160的N进制计数器设计

五、相关课程:《数字电子技术》,点击学习课程

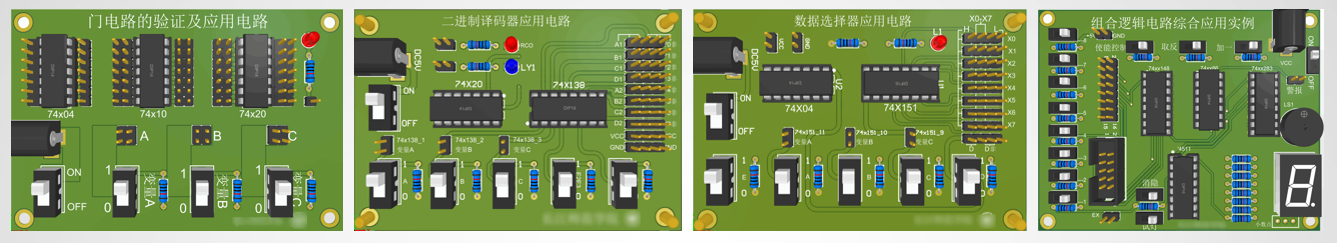

《数字电子技术》是电子信息类、电气类、自动化类、计算机类等专业的一门专业基础课,同时也是一门重要工程技术课程,是研究数字系统设计的入门课程。本课程主要讲述数字技术和数字系统的基本概念、基本原理和基本技能,重在培养工程实践能力。本课程讲授特色:借助Logisim软件处理逻辑运算,使用Proteus完成逻辑电路的虚拟仿真,基于Quartus II展示了现代方法设计数字电路的流程和操作。具体学习内容包括:

数制与码制

逻辑代数基础

逻辑门电路

组合逻辑电路的分析与设计

锁存器和触发器

时序逻辑电路的分析与设计

脉冲产生电路

模数转换和数模转换

可编程逻辑器件

硬件描述语言简介(Verilog HDL)

基于EDA的组合逻辑电路设计综合验证

基于EDA的时序逻辑电路设计综合验证

数字电子技术实验实训